High-Performance and Energy-Efficient In-Order Cores

Implemented the Freeflow and Load-Slice in-order core designs which help increase performance and energy efficiency

Guide: Prof. Virendra Singh

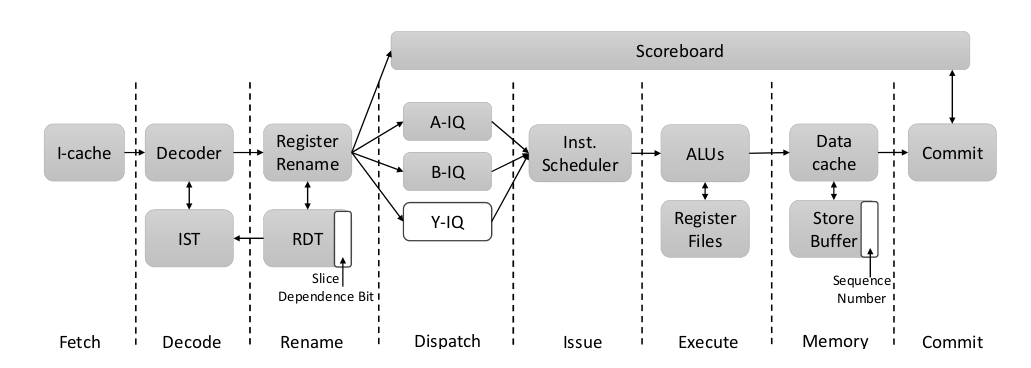

Sliced-Out-of-Order processors propose an energy-efficient architecture which add just enough OoO support for MLP extraction. The state of the art sOoO core, Load-Slice Core increase energy efficiency by 43% over in-order cores and 4.7x over out-of-order cores. Freeway uses a new dependence-aware slice execution policy that tracks dependent slices and keeps them out of the way of MLP extraction. This helps it perform 12% faster than traditional sOoO cores and with minimal hardware/energy overheads. Freeflow core also proposes modifications on top of traditional sOoO cores which help extract the inherent ILP in the program, rather than focusing on MLP extraction in the case of Freeway. I have sucessfully implemented the Load-Slice and Freeflow core architectures using the Gem5 multicore simulator.

References

2019

- Freeflow Core: Enhancing Performance of In-Order Cores with Energy EfficiencyIn 2019 IEEE 37th International Conference on Computer Design (ICCD), Aug 2019

- Freeway: Maximizing MLP for Slice-Out-of-Order ExecutionIn 2019 IEEE International Symposium on High Performance Computer Architecture (HPCA), Aug 2019

2015

- The Load Slice Core microarchitectureIn 2015 ACM/IEEE 42nd Annual International Symposium on Computer Architecture (ISCA), Aug 2015