FPGA Accelerator for SNNs

Implemented and simulated an FPGA-based accelerator for Spiking Neural Networks

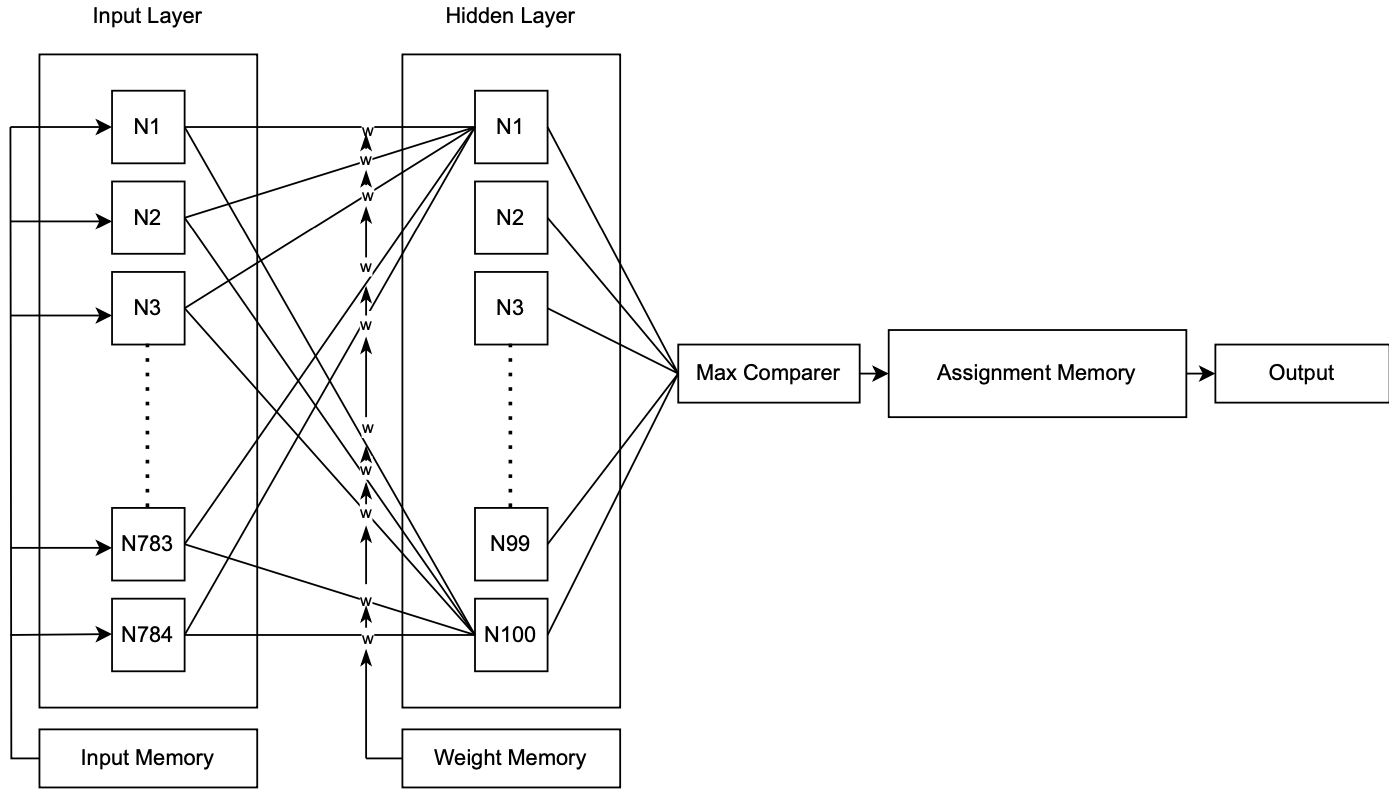

Overview of the designed Spiking Neural Network flow

Guide: Prof. Sachin Patkar

This project was taken up as part of the course EE705: VLSI Design Lab by Prof. Sachin Patkar. The problem statement was to implement an FPGA-based accelerator for spiking neural networks. We designed an SNN flow graph with 784 input neurons and 100 hidden layer neurons. The input neurons were fed the MNIST images (encoded as a spike train) and finally the hidden layer neuron with the most spikes was used for classifying the image. The project involved the use of ROM IPs to store the input image, neuron weights, and the assignment mapping.