RISC Processor Design

Designed and implemented 16-bit 6-stage pipelined processor in VHDL

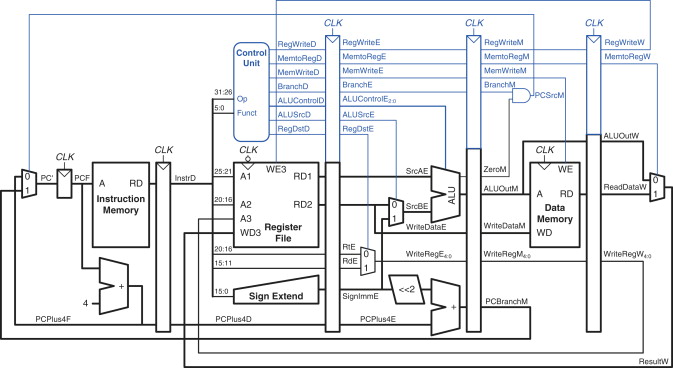

Overview of a 6-stage pipeline processor

Guide: Prof. Virendra Singh

This was a course project as part of the course EE309: Microprocessors taught by Prof. Virendra Singh. The project involved designing a 6-stage Pipelined processor, capable of running a Turing-complete ISA of 17 instructions. Ours was one of the few teams to optimize the processor using hazard mitigation techniques, forwarding logic, and branch prediction techniques. We also performed software testing for all the instructions using the Intel Quartus Environment and the ModelSim HDL simulator.