## EE619: Project-II

Anubhav Bhatla, 200070008

April 21, 2024

#### Design for Cross-coupled Oscillator

In order to limit the power below 3mW, we can take I to be **2mA**. Say we choose  $L_1 = L_2 = 1$ nH (if we use a centre-tapped inductor: L = 2nH). The oscillation frequency is given as follows:

$$2\pi \times f_{osc} = \frac{1}{\sqrt{L_1(C_1 + C_{var})}}$$

For an oscillation frequency of 6GHz, we get  $C_1 + C_{var} = 700 fF$ . Say we choose  $C_{var} = 20 fF$  and  $C_1 = C_2 = 680 fF$ .

We can choose a width W = 3200nm for  $M_0$  and  $M_1$  in order to get nearly complete current switching with  $V_{swing}$ .

In order to scale  $I_{BIAS}$  to I requires a width ratio of  $I/I_{BIAS} = 10$ . Therefore we can use  $W = 10 \mu m$  and  $1 \mu m$  for  $M_2$  and  $M_3$  respectively.

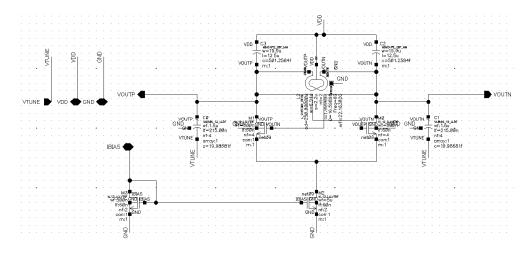

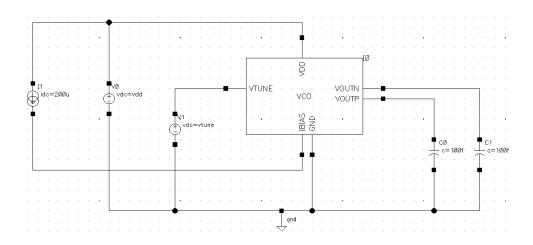

Table 1 summarizes the final component parameters used. Figure 1 shows the schematic of the VCO along with component parameter annotations and 2 shows the schematic for the testbench used.

| MOS Devices        | Finger Width      | Length           | Multipliers | Fingers           |

|--------------------|-------------------|------------------|-------------|-------------------|

| $M_0$              | 800nm             | $60 \mathrm{nm}$ | 1           | 4                 |

| $M_1$              | 800m              | $60 \mathrm{nm}$ | 1           | 4                 |

| $M_2$              | $5\mu\mathrm{m}$  | $60 \mathrm{nm}$ | 1           | 2                 |

| $M_3$              | $500 \mathrm{nm}$ | $60 \mathrm{nm}$ | 1           | 2                 |

| Passive Components |                   |                  |             | Value             |

| L                  |                   |                  |             | 2nH               |

| $C_0$              |                   |                  |             | 20fF              |

| $C_1$              |                   |                  |             | $20\mathrm{fF}$   |

| $C_2$              |                   |                  |             | $501 \mathrm{fF}$ |

| $C_3$              |                   |                  |             | 501fF             |

| I <sub>BIAS</sub>  |                   |                  |             | $200\mu A$        |

| V <sub>DD</sub>    |                   |                  |             | 1.2V              |

Table 1: Component parameters used for the VCO.

# 1 Schematic

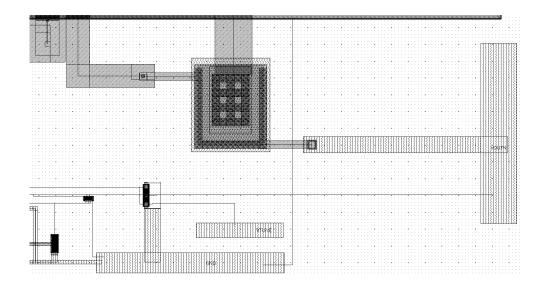

Figure 1: Schematic for the VCO with component parameter annotations.

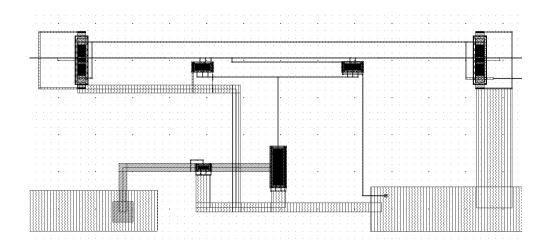

Figure 2: Schematic for the VCO testbench.

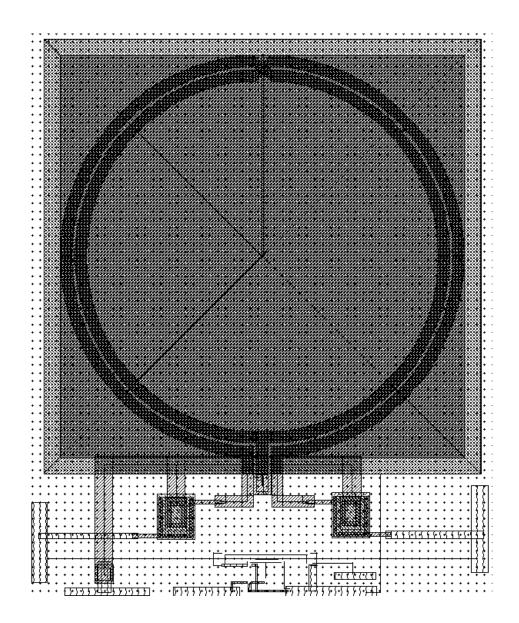

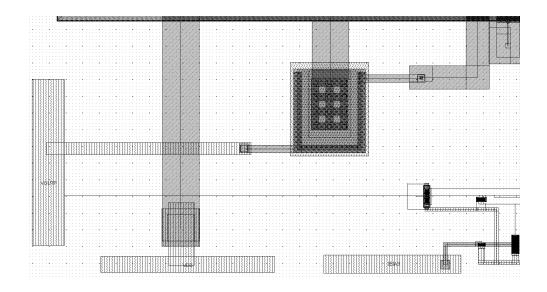

# 2 Layout

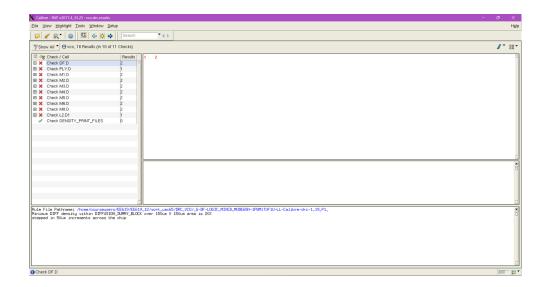

## 3 DRC

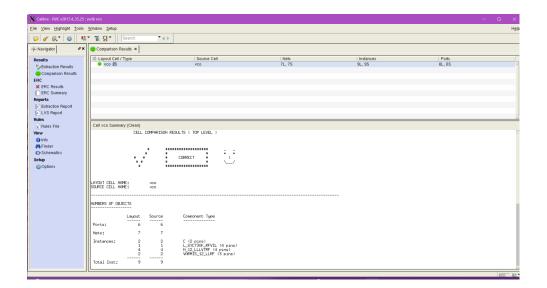

## 4 LVS

#### 5 Transient

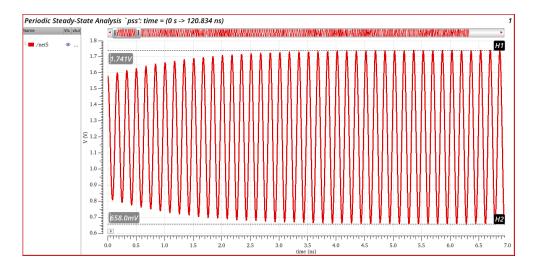

Figure 3 shows the transient signal at the output node of the designed VCO. Here, we can see that we have a peak-to-peak voltage swing of around  $1.083V_{pp}$ , which meets the required specification.

Figure 3: Transient signal at the output node of the VCO.

### 6 Frequency Tuning

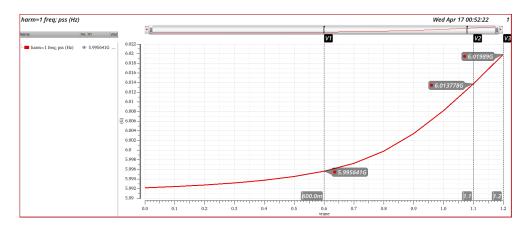

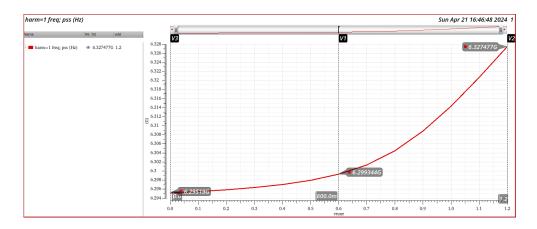

Figure 4 shows the variation of oscillator frequency as  $V_{tune}$  varies from 0 to 1.2V. We can observe a tuning range of about **28MHz**. We also observe a max  $K_{VCO}$  value of around **61MHz/V**, which is within the required specification. From the schematic simulations, we can observe that the oscillation frequency at  $V_{TUNE} = 0.6V$  is around **6.3GHz** and the tuning range is higher, at around **32MHz**. This is because of parasitic capacitances considered in the post-layout simulations, which reduce the oscillation frequency and the tuning range.

Figure 4: Plot for frequency as  $V_{tune}$  varies in post-layout simulations.

Figure 5: Plot for frequency as  $V_{tune}$  varies in schematic simulations.

### 7 Phase Noise

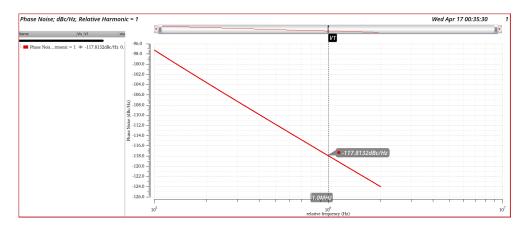

Figure 6 shows the phase noise (in dBc) for the designed LNA circuit. The phase noise at a relative frequency of 1MHz is close to -117dBc/Hz, which meets the desired specification.

Figure 6: Phase Noise (in dBc) for the designed VCO circuit.

### 8 Variation with $V_{DD}$

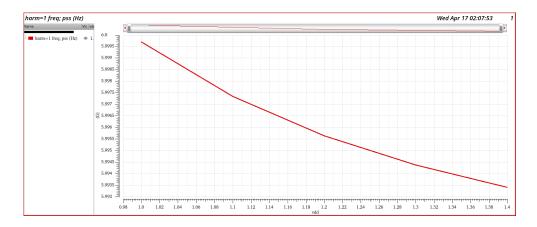

Figure 7 shows the variation of oscillator frequency as  $V_{tune}$  varies from 1.0 to 1.4V. As we increase  $V_{DD}$ , the  $V_{GS}$  of the varactors  $M_2$ ,  $M_3$  increases. Due to this the capacitance of the varactors also increases as we increase  $V_{DD}$ . This leads to a decrease in the oscillation frequency.

Figure 7: Plot for frequency as  $V_{DD}$  varies.